# 260Pin DDR4 3200 1.2V ECC SO-DIMM 16GB Based on 1024Mx8 AQD-SD4U16GE32-SE

## **Description**

AQD-SD4U16GE32-SE is a DDR4 3200Mbps ECC SO-DIMM high-speed, memory module that use 18pcs of 1024M x 8 bits DDR4 SDRAM in FBGA package and a 4K bits serial EEPROM on a 260-pin printed circuit board. AQD-SD4U16GE32-SE is a Dual In-Line Memory Module and is intended for mounting into 260-pin edge connector sockets.

Synchronous design allows precise cycle control with the use of system clock. Data I/O transactions are possible on both edges of DQS. Range of operation frequencies, programmable latencies allow the same device to be useful for a variety of high bandwidth, high performance memory system applications.

#### **Features**

- RoHS compliant products.

- JEDEC standard 1.2V(1.14V~1.26V) Power supply

VDDQ= 1.2V(1.14V~1.26V)

- VPP = 2.5V +0.25V / -0.125V

- Data transfer rates: PC4-3200

Programmable CAS Latency:10~22

- 8 bit pre-fetch

- Burst Length (BL) switch on-the-fly BL8 or BC4

- Bi-directional Differential Data-Strobe

- On Die Termination, Nominal, Park, and Dynamic ODT

- Serial presence detect with EEPROM

Asynchronous reset

PCB edge connector treated with 30u" Gold-Plating

- · Anti sulfur resistor used

### Pin Identification

| Symbol                        | Function               |

|-------------------------------|------------------------|

| A0-A17 <sup>1</sup> , BA0~BA1 | Address/Bank input     |

| DQ0~DQ63                      | Bi-direction data bus. |

| DOS0 + DOS17 +      | Data Buffer data strobes                 |

|---------------------|------------------------------------------|

| DQS0_t-DQS17_t      | Data Buffer data strobes                 |

| DQS0_c-DQS17_c      |                                          |

| CK0_t, CK1_t        | Register clock input                     |

| CK0_c, CK1_c        | Registert clocks input                   |

| ODT0 &ODT1          | On-die termination control line          |

| CS0_n-CS3_n         | DIMM Rank Select Lines input.            |

| RAS_n²              | Row address strobe                       |

| CAS_n³              | Column address strobe                    |

| WE_n <sup>4</sup>   | Write Enable                             |

| DM0~DM7             | Data masks/high data strobes             |

| VDD                 | Core power supply                        |

| VDDQ                | I/O driver power supply                  |

| V <sub>REF</sub> CA | Command/address reference supply         |

| V <sub>DD</sub> SPD | SPD EEPROM power supply                  |

| SA0~SA2             | I2C serial bus address select for        |

|                     | EEPROM                                   |

| SCL                 | I2C serial bus clock for EEPROM          |

| SDA                 | I2C serial bus data for EEPROM           |

| VSS                 | Ground                                   |

| RESET_n             | Set DRAMs Known State                    |

| VTT                 | DRAM I/O termination supply              |

| VPP                 | SDRAM Supply                             |

| ALERT_n             | Register ALERT_n output                  |

| EVENT_n             | SPD signals a thermal event has occurred |

| RFU                 | Reserved for future use                  |

<sup>1.</sup> Address A17 is only valid for 16 Gb x4 based SDRAMs.

<sup>2.</sup> RAS\_n is a multiplexed function with A16.

<sup>3.</sup> CAS\_n is a multiplexed function with A15.

<sup>4.</sup> WE\_n is a multiplexed function with A14.

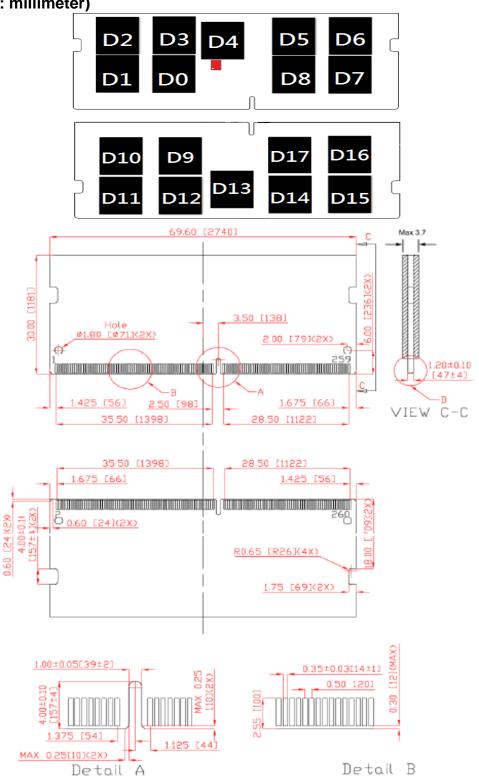

## **Dimensions (Unit: millimeter)**

Note:1. Tolerances on all dimensions +/-0.15mm unless otherwise specified.